# **Compiler Design**

Lecture 16: Liveness Analysis

Christophe Dubach Winter 2021

Some material from Prof. Michelle Strout, CS553, Colorado State University.

Timestamp: 2021/03/10 13:19:42

Example of generated MIPS code (using virtual registers):

| 4   |                                                           |  |

|-----|-----------------------------------------------------------|--|

| 4   |                                                           |  |

|     |                                                           |  |

|     |                                                           |  |

| v0, | x                                                         |  |

| v1, | ( <b>v</b> 0)                                             |  |

| v2, | v0, v1                                                    |  |

| v3, | У                                                         |  |

| v4, | ( <b>v3</b> )                                             |  |

| v5, | v4, v2                                                    |  |

| v6, | v2, v4                                                    |  |

| v5, | ( <b>v</b> 0)                                             |  |

| v6, | ( <b>v3</b> )                                             |  |

|     | 4<br>v0,<br>v1,<br>v2,<br>v3,<br>v4,<br>v5,<br>v6,<br>v5, |  |

After "proper" register allocation (possible output):

| .data     |       |            |

|-----------|-------|------------|

| x: .space | 4     |            |

| y: .space | 4     |            |

|           |       |            |

| .text     |       |            |

| la        | \$t0, | x          |

| lw        | \$t1, | (\$t0)     |

| add       | \$t2, | \$t0, \$t1 |

| la        | \$t3, | У          |

| lw        | \$t4, | (\$t3)     |

| sub       | \$t5, | \$t4, \$t2 |

| add       | \$t6, | \$t2, \$t4 |

| SW        | \$t5, | (\$t0)     |

| SW        | \$t6, | (\$t3)     |

|           |       |            |

What if less than 7 architectural registers available for allocation?

• Need to know which values is going to be used in the future.

## Definition

A variable (virtual register) is live at some point in the program if it has previously been defined by an instruction and will be used by an instruction in the future. It is dead otherwise.

Q Two variables can use the same architectural register if they are never used at the same time, *i.e.* never simulataneously live.

$\Rightarrow$  Register allocation use liveness information.

# Example:

| .data       |               |                         |

|-------------|---------------|-------------------------|

| x: .space 4 | 4             |                         |

| y: .space 4 | 4             |                         |

| .text       |               | Live after instruction: |

| la v        | <b>v0</b> , x | vO                      |

| lw v        | v1, (v0)      | v0 v1                   |

| add v       | v2, v1, v1    | v0 v2                   |

| la v        | <b>v3</b> , y | v0 v2 v3                |

| lw v        | v4, (v3)      | v0 v2 v3 v4             |

| sub v       | v5, v4, v2    | v0 v2 v3 v4 v5          |

| add v       | v6, v2, v4    | v0 v3 v5 v6             |

| sw v        | v5, (v0)      | v3 v6                   |

| sw v        | v6, (v3)      |                         |

Question: how many architectural registers are needed?

Computing liveness is more complicated in the presence of control flow (e.g. loops, if-then-else).

Assembly pseudo-code: <sup>1</sup>

a = 0L1: b = a + 1 c = c + b a = b\*2 if (a<9) goto L1 return c

Question: what is the live range of b?

To answer this question we need to understand the dynamic flow of the program execution.

<sup>&</sup>lt;sup>1</sup>We illustrate concepts at a slightly higher level than assembly from this point on.

# Control-Flow Graph (CFG)

## Concept invented in 1970 by:

# Frances Allen (1932–2020), IBM, (1st woman to receive Turing Award in 2006!)

source: Rama, CC BY-SA 2.0 FR, wikimedia

## Directed graph:

## What is the live range of b?

- b is used in statement 4, so b is live on the  $3 \rightarrow 4$  edge

- since statement 3 does not define b, b is also live on the 2  $\rightarrow$  3 edge

- statement 2 defines b, so any value of b on the 1 → 2 and 5 → 2 edges are not needed, so b is dead along these edges

b live range is  $2 \rightarrow 3 \rightarrow 4$

Live range of a:

•  $1\rightarrow 2 \text{ and } 4\rightarrow 5\rightarrow 2$

Live range of b:

•  $2 \rightarrow 3 \rightarrow 4$

Live range of c:

• entry  $\rightarrow$  1  $\rightarrow$  2  $\rightarrow$  3  $\rightarrow$  4  $\rightarrow$  5  $\rightarrow$  2 and 5  $\rightarrow$  6

${f Q}$  Since a and b never simultaneously live, can share a register.

# Terminology

# Flow Graph

- a Control Flow Graph (CFG) has out-edges that leads to successor nodes and in-edges that come from predecessor nodes

- pred(n) = set of all predecessors of node n succ(n) = set of all successors of node n

#### Examples

- Out-edges of node 5:  $5 \rightarrow 6$  and  $5 \rightarrow 2$

- $succ(5) = \{2,6\}$

- $pred(5) = \{4\}$

- $pred(2) = \{1,5\}$

# Def (definition)

- A write of a value to a variable

- def(v) = set of CFG nodes that define variable v

- def(n) = set of variables defined at node n

# Use

- A read of a variable's value

- use(v) = set of CFG nodes that use variable v

- use(n) = set of variables used at node n

| 5: | а | < | 9 |

|----|---|---|---|

|----|---|---|---|

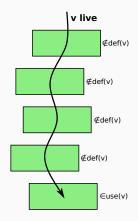

## A variable v is live on a CFG edge if

- $\exists$  a directed path from that edge to a use of v (node  $\in$  use(b)) and

- that path does not go through any def of v (nodes ∉ def(v).

# **Computing Liveness**

# Data-flow

• Liveness of variables is a property that flows through the edges of the CFG

# Direction of flow

• Liveness flows backward in the CFG: behaviour of future nodes determines liveness at a given node

### Example: flow of liveness for a

Example: flow of liveness for b

## We have liveness on edges

• before and after each node

## Two more definitions:

- A variable is live-out at a node if it is live on any of that node's out-edges

- A variable is live-in at a node if it is live on any of that node's in-edges

# **Computing Liveness**

## Rules for computing liveness

1. Generate liveness:

$v \in use(n) \Rightarrow v \in LIVE_{in}(n)$

- Push liveness across edges:

v ∈ LIVE<sub>in</sub>(n) ⇒ ∀<sub>p∈pred(n)</sub>v ∈ LIVE<sub>out</sub>(p)

- 3. Push liveness across nodes:  $v \in \text{LIVE}_{out}(n) \land v \notin def(n) \Rightarrow v \in \text{LIVE}_{in}(n)$

### **Data-flow equations**

$$LIVE_{in}(n) = use(n)_{1} \cup (LIVE_{out}(n) - def(n))_{3}$$

$$LIVE_{out}(n) = \bigcup_{\forall s \in succ(n)} LIVE_{in}(s)_{2}$$

1: for all node  $n \in \mathsf{CFG}$  do

2:

$$\operatorname{LIVE}_{in}(n) = \emptyset$$

- 3:  $\operatorname{LIVE}_{out}(n) = \emptyset$

- 4: end for

- 5: repeat

- 6: for all node  $n \in CFG$  do

7:

$$\operatorname{LIVE}_{in}^{\prime}(n) = \operatorname{LIVE}_{in}(n)$$

- 8:  $LIVE'_{out}(n) = LIVE_{out}(n)$

- 9:  $\operatorname{LIVE}_{in}(n) = use(n) \cup (\operatorname{LIVE}_{out}(n) def(n))$

10:

$$\operatorname{LIVE}_{out}(n) = \bigcup_{\forall s \in succ(n)} \operatorname{LIVE}_{in}(s)$$

### 11: end for

12: **until**  $\text{LIVE}'_{in}(n) = \text{LIVE}_{in}(n) \land \text{LIVE}'_{out}(n) = \text{LIVE}_{out}(n) \forall n$

This is a fix-point algorithm for iterative liveness analysis.

# Example

| node | use | def |    |     | 2nd |     |    |     |    |     |    |     |    |     | 7th |     |

|------|-----|-----|----|-----|-----|-----|----|-----|----|-----|----|-----|----|-----|-----|-----|

|      |     |     | in | out | in  | out | in | out | in | out | in | out | in | out | in  | out |

| 1    |     | а   |    |     |     | а   |    |     |    | ac  |    |     |    |     |     |     |

| 2    | а   | b   | а  |     | а   | bc  | ac | bc  | ac | bc  | ac | bc  | ас | bc  | ac  | bc  |

| 3    | bc  | с   | bc |     | bc  | b   | bc | b   | bc | b   | bc | b   | bc | bc  | bc  | bc  |

| 4    | b   | а   | b  |     | b   | а   | b  | а   | b  | ас  | bc | ас  | bc | ас  | bc  | ac  |

| 5    | а   |     | а  | а   | а   | ac  | ac | ac  | ac | ас  | ac | ас  | ас | ас  | ac  | ac  |

| 6    | с   |     | с  |     | с   |     | с  |     | с  |     | с  |     | с  |     | с   |     |

#### **Data-flow equations**

$$\begin{split} \text{LIVE}_{in}(n) &= use(n) \cup (\text{LIVE}_{out}(n) - def(n)) \\ \text{LIVE}_{out}(n) &= \bigcup_{\forall s \in succ(n)} \text{LIVE}_{in}(s) \end{split}$$

There is something inefficient about this process.

For instance, consider the  $3 \rightarrow 4$  edge in the graph:

- $LIVE_{out}(4)$  is used to compute  $LIVE_{in}(4)$

- $LIVE_{in}(4)$  is used to compute  $LIVE_{out}(3)$

<sup>1</sup> The algorithm would converge faster if we process the nodes backwards.

- 1: for all node  $n \in \mathsf{CFG}\ensuremath{\mbox{do}}$

- 2:  $\operatorname{LIVE}_{in}(n) = \emptyset$

- 3:  $\operatorname{LIVE}_{out}(n) = \emptyset$

- 4: end for

- 5: repeat

- 6: for all node  $n \in CFG$  in reverse topological order do

- 7:  $\operatorname{LIVE}_{in}^{\prime}(n) = \operatorname{LIVE}_{in}(n)$

- 8:  $\operatorname{LIVE}'_{out}(n) = \operatorname{LIVE}_{out}(n)$

- 9:  $\operatorname{LIVE}_{out}(n) = \bigcup_{\forall s \in \operatorname{succ}(n)} \operatorname{LIVE}_{in}(s)$

- 10:  $\operatorname{LIVE}_{in}(n) = use(n) \cup (\operatorname{LIVE}_{out}(n) def(n))$

- 11: end for

12: **until**  $\text{LIVE}'_{in}(n) = \text{LIVE}_{in}(n) \land \text{LIVE}'_{out}(n) = \text{LIVE}_{out}(n) \forall n$

# Example with Backward Liveness Analysis

True

| node | use | def | 1st |    |                |    |     |    |  |

|------|-----|-----|-----|----|----------------|----|-----|----|--|

|      |     |     | out | in | out            | in | out | in |  |

| 6    | С   |     |     | С  | ac<br>ac<br>bc | С  |     | С  |  |

| 5    | а   |     | с   | ac | ас             | ас | ас  | ас |  |

| 4    | b   | а   | ас  | bc | ас             | bc | ас  | bc |  |

| 3    | bc  | С   | bc  | bc | bc             | bc | bc  | bc |  |

| 2    | а   | b   | bc  | ac | bc             | ac | bc  | ac |  |

| 1    |     | а   | ас  | С  | ас             | с  | ас  | с  |  |

Converges in only 3 iterations!

**Data-flow equations**

$$\begin{split} \text{LIVE}_{out}(n) &= \bigcup_{\forall s \in succ(n)} \text{LIVE}_{in}(s) \\ \text{LIVE}_{in}(n) &= use(n) \cup (\text{LIVE}_{out}(n) - def(n)) \end{split}$$

#### **Basic Block**

A straight sequence of assembly instruction which (usually) finishes with a branch/jump instruction.

Key property: Either *all* the instructions in the sequence execute or none execute.

Can significantly decrease the size that a CFG occupies in memory by grouping nodes that have a single predecessor and a single successor into basic blocks.

The instructions in a basic block can be simply represented as a list (rather than a graph).

# Example

No basic blocks:

With basic blocks:

• Proper register allocation