# Compiler Design

Lecture 16: Liveness Analysis

Christophe Dubach Winter 2023

Some material from Prof. Michelle Strout, CS553, Colorado State University.

Timestamp: 2023/03/05 15:35:00

# Proper register allocation

Assign each virtual register to an architectural register (if possible).

#### Example using virtual registers:

```

.data

x: .space 4

y: .space 4

.text

la v0, x

lw v1, (v0)

add v2, v0, v1

la v3, y

lw v4. (v3)

sub v5, v4, v2

add v6, v2, v4

sw v5, (v0)

sw v6. (v3)

```

#### After "'proper" register allocation:

```

.data

x: .space 4

y: .space 4

.text

la $t0, x

lw $t1, ($t0)

add $t2, $t0, $t1

la $t3, y

lw $t4, ($t3)

sub $t5, $t4, $t2

add $t6, $t2, $t4

sw $t5, ($t0)

sw $t6, ($t3)

```

#### Problem:

What if more virtual registers used than the number of architectural registers available?

#### Solution:

- 🕹 Re-cycle architectural registers.

- $\cdot \Rightarrow$  Need to know which values is going to be used in the future.

#### Terminology

From now on in this lecture, we will use the term *variable* to denote a *virtual register*.

#### Liveness

#### Definition

A variable (virtual register) is <u>live</u> at some point in the program if it has previously been <u>defined</u> by an instruction and will be <u>used</u> by an instruction in the future. It is <u>dead</u> otherwise.

- Two variables can use the same architectural register if they are never used at the same time, *i.e.* never simulataneously live.

- $\Rightarrow$  Register allocation use liveness information.

#### Example:

```

.data

x: .space 4

y: .space 4

Live after instruction:

.text

la v0, x

vΘ

lw v1, (v0)

v0 v1

add v2, v1, v1

v0 v2

la v3, y

v0 v2 v3

lw v4, (v3)

v0 v2 v3 v4

add v6, v2, v4

v3 v5 v6

v0

sw v5, (v0)

v3

v6

sw v6, (v3)

```

Question: what is the minimum number of architectural registers needed?

Computing liveness is more complicated in the presence of control flow (e.g. loops, if-then-else).

## Assembly pseudo-code: 1

```

a = 0

L1: b = a + 1

c = c + b

a = b*2

if (a<9) goto L1

return c

```

Question: what is the live range of b?

To answer this question we need to understand the dynamic flow of the program execution.

<sup>&</sup>lt;sup>1</sup>We illustrate concepts at a slightly higher level than assembly from this point on.

# Control-Flow Graph (CFG)

## Concept invented in 1970 by:

Frances Allen (1932–2020), IBM, (1st woman to receive Turing Award in 2006!)

source: Rama, CC BY-SA 2.0 FR, wikimedia

```

a = 0

L1: b = a + 1

c = c + b

a = b*2

if (a<9) goto L1

return c

```

## Directed graph:

## What is the live range of b?

- b is used in statement 4, so b is live on the 3 → 4 edge

- since statement 3 does not define **b**, **b** is also live on the  $2 \rightarrow 3$  edge

- statement 2 defines b, so any value of b on the 1 → 2 and 5 → 2 edges are not needed, so b is dead along these edges

b live range is  $2 \rightarrow 3 \rightarrow 4$

## Live range of a:

• 1

$$\rightarrow$$

2 and 4  $\rightarrow$  5  $\rightarrow$  2

## Live range of b:

•

$$2 \rightarrow 3 \rightarrow 4$$

#### Live range of c:

• entry

$$\rightarrow$$

1  $\rightarrow$  2  $\rightarrow$  3  $\rightarrow$  4  $\rightarrow$  5  $\rightarrow$  2 and 5  $\rightarrow$  6

${\mathfrak Q}$  Since **a** and **b** never simultaneously live, can share a register.

# Terminology

#### Flow Graph

- a Control Flow Graph (CFG) has out-edges that leads to successor nodes and in-edges that come from predecessor nodes

- pred(n) = set of all predecessors of node n succ(n) = set of all successors of node n

#### **Examples**

- Out-edges of node 5: 5  $\rightarrow$  6 and 5  $\rightarrow$  2

- $succ(5) = \{2,6\}$

- $pred(5) = \{4\}$

- $pred(2) = \{1,5\}$

#### **Uses and Defs**

## Def (definition)

- · A write of a value to a variable

- def(v) = set of CFG nodes that define variable v

- def(n) = set of variables defined at node n

#### Use

- · A read of a variable's value

- use(v) = set of CFG nodes that use variable  $\mathbf{v}$

- use(n) = set of variables used at node n

# More precise definition of liveness

## A variable v is live on a CFG edge if

- ∃ a directed path from that edge to a use of v (node ∈ use(b)) and

- that path does not go through any def of v (nodes ∉ def(v)).

# Computing Liveness

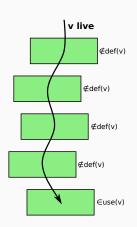

## Flow of Liveness

#### Data-flow

• Liveness of variables is a property that flows through the edges of the CFG

#### Direction of flow

Liveness flows backward in the CFG: behaviour of future nodes determines liveness at a given node

## Example: flow of liveness for a

#### Example: flow of liveness for b

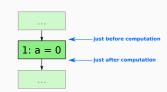

## Liveness at Nodes

#### We have liveness on edges

· before and after each node

#### Two more definitions:

- A variable is live-out at a node if it is live on any of that node's out-edges

- A variable is live-in at a node if it is live on any of that node's in-edges

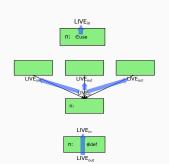

# **Computing Liveness**

## Rules for computing liveness

- 1. Generate liveness:

- $v \in use(n) \Rightarrow v \in LIVE_{in}(n)$

- 2. Push liveness across edges:

$$v \in LIVE_{in}(n) \Rightarrow \forall_{p \in pred(n)} v \in LIVE_{out}(p)$$

3. Push liveness across nodes:

$$v \in LIVE_{out}(n) \land v \notin def(n) \Rightarrow v \in LIVE_{in}(n)$$

This is called the transfer function

#### Data-flow equations

$$LIVE_{in}(n) = \underbrace{use(n)}_{1} \cup \underbrace{(LIVE_{out}(n) - def(n))}_{2}$$

$$LIVE_{out}(n) = \underbrace{\bigcup_{\forall s \in succ(n)} LIVE_{in}(s)}_{2}$$

# Solving the Data-flow equations

```

1. for all node n \in CFG do

2: LIVE<sub>in</sub>(n) = \varnothing

3: LIVE<sub>out</sub>(n) = \varnothing

4: end for

5: repeat

for all node n \in CFG do

LIVE'_{in}(n) = LIVE_{in}(n)

LIVE'_{out}(n) = LIVE_{out}(n)

LIVE_{in}(n) = use(n) \cup (LIVE_{out}(n) - def(n))

9.

LIVE_{out}(n) = \bigcup LIVE_{in}(s)

10:

\forall s \in succ(n)

end for

11:

12: until LIVE'<sub>in</sub>(n) = LIVE<sub>in</sub>(n) \wedge LIVE'<sub>out</sub>(n) = LIVE<sub>out</sub>(n)\foralln

```

This is a fix-point algorithm for iterative liveness analysis.

## Example

| node        | use     |   |    |     | 2nd |     |    |     |    |     |    |     |    |     |    |     |  |

|-------------|---------|---|----|-----|-----|-----|----|-----|----|-----|----|-----|----|-----|----|-----|--|

|             |         |   | in | out | in  | out | in | out | in | out | in | out | in | out | in | out |  |

| 1           | a<br>bc | a |    |     |     | a   |    | а   |    | ac  | С  | ac  | С  | ac  | С  | ac  |  |

| 1<br>2<br>3 | a       | b | а  |     | a   | bc  | ac | bc  |  |

| 3           | bc      | C | bc |     | bc  | b   | bc | b   | bc | b   | bc | b   | bc | bc  | bc | bc  |  |

|             | b       | a | b  |     | b   | а   | b  | a   | b  | ac  | bc | ac  | bc | ac  | bc | ac  |  |

| 4<br>5<br>6 | a       |   | а  | a   | a   | ac  | ac | ac  |  |

| 6           | C       |   | C  | a   | С   |     | C  |     | C  |     | С  |     | C  |     | C  |     |  |

#### Data-flow equations

$$LIVE_{in}(n) = use(n) \cup (LIVE_{out}(n) - def(n))$$

$$LIVE_{out}(n) = \bigcup_{\forall s \in succ(n)} LIVE_{in}(s)$$

There is something inefficient about this process.

For instance, consider the  $3 \rightarrow 4$  edge in the graph:

- LIVE<sub>out</sub>(4) is used to compute LIVE<sub>in</sub>(4)

- LIVE<sub>in</sub>(4) is used to compute LIVE<sub>out</sub>(3)

The algorithm would converge faster if we process the nodes backwards.

# Backward Liveness Analysis

```

1: for all node n \in CFG do

2: LIVE<sub>in</sub>(n) = \varnothing

3: LIVE<sub>out</sub>(n) = \varnothing

4 end for

5: repeat

for all node n \in CFG in reverse pre-order do

LIVE'_{in}(n) = LIVE_{in}(n)

7.

LIVE'_{out}(n) = LIVE_{out}(n)

8.

LIVE_{out}(n) = \bigcup LIVE_{in}(s)

9:

\forall s \in succ(n)

LIVE_{in}(n) = use(n) \cup (LIVE_{out}(n) - def(n))

10.

end for

11:

12: until LIVE'_{in}(n) = LIVE_{in}(n) \wedge LIVE'_{out}(n) = LIVE_{out}(n)\foralln

```

# Example with Backward Liveness Analysis

| node | use | def | 19  | st | 2n       | d  | 3rd |    |  |

|------|-----|-----|-----|----|----------|----|-----|----|--|

|      |     |     | out | in | out      | in | out | in |  |

| 6    | С   |     |     | С  | ac<br>ac | С  |     | С  |  |

| 5    | a   |     | С   | ac | ac       | ac | ac  | ac |  |

| 4    | b   | a   | ac  | bc | ac       | bc | ac  | bc |  |

| 3    | bc  | C   | bc  | bc | bc       | bc | bc  | bc |  |

| 2    | a   | b   | bc  | ac | bc       | ac | bc  | ac |  |

| 1    |     | а   | ac  | С  | ac       | С  | ac  | С  |  |

#### Converges in only 3 iterations!

#### Data-flow equations

$$\begin{aligned} \mathsf{LIVE}_{out}(n) &= \bigcup_{\forall s \in \mathsf{succ}(n)} \mathsf{LIVE}_{in}(s) \\ \mathsf{LIVE}_{in}(n) &= \mathsf{use}(n) \cup (\mathsf{LIVE}_{out}(n) - \mathsf{def}(n)) \end{aligned}$$

# More performance considerations

#### Basic Block

A straight sequence of assembly instruction which (usually) finishes with a branch/jump instruction.

Key property: Either *all* the instructions in the sequence execute or none execute.

Can significantly decrease the size that a CFG occupies in memory by grouping nodes that have a single predecessor and a single successor into basic blocks.

The instructions in a basic block can be simply represented as a list (rather than a graph).

# Example

#### No basic blocks:

#### With basic blocks:

$$use(2) = \{a, c\}$$

$def(2) = \{a, b, c\}$

## Next lecture

• Proper register allocation